Microsemi Libero学习和使用笔记

一、下载和安装

下载和安装可以参考以下教程。其中申请license的步骤推荐使用临时邮箱,其他的信息可以随便填。

二、初步使用(教程)

(1)创建工程

- 首先新建工程,路径不要带中文,然后选择芯片型号为

AGL250V2-VQ100。 - 选择IO的电平标准,不同的电平标准,高低电平的电压范围是不同的,这里选择默认的LVTTL。

- 是否创建MSS模块,MSS里有PLL和ARM Cortex-M3的使用,以后用到PLL和ARM核时再添加,这里先不选择,以后需要也可以再创建。

- 是否导入已经存在的HDL文件,如果已经有一些写好的模块,可以在这里直接导入。是否导入已经存在的管脚约束文件,这里选择不添加,我们会在后面通过图形化工具来指定管脚。

- 除了第一步以外其他的选项可以先不选,一路Next创建工程。

创建好的工程如下:

创建好的工程子文件夹及其功能如下:

(2)添加设计文件

创建Verilog文件有多种方式,可以直接双击左侧菜单中的

Create Design->Create HDL添加源代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43///////////////////////////////////////////////////////////////////////////////////////////////////

// Company: <Name>

//

// File: pwm.v

// File history:

// <Revision number>: <Date>: <Comments>

// <Revision number>: <Date>: <Comments>

// <Revision number>: <Date>: <Comments>

//

// Description:

//

// <Description here>

//

// Targeted device: <Family::IGLOO> <Die::AGL250V2> <Package::100 VQFP>

// Author: <Name>

//

///////////////////////////////////////////////////////////////////////////////////////////////////

//`timescale <time_units> / <precision>

module pwm( clk, rst_n, ja1 );

input clk, rst_n;

output ja1;

reg [2:0] cnt_freq;

reg freq;

always @(posedge clk or negedge rst_n) begin //20MHz

if(!rst_n) begin

cnt_freq <= 0;

freq <= 0;

end

else begin

cnt_freq <= cnt_freq + 1;

if(cnt_freq < 3) freq <= 0;

else begin

freq <= 1;

if(cnt_freq == 4) cnt_freq <= 0;//cnt_freq=0,1,2,freq=0;cnt_freq=3,freq=1

end

end

end

assign ja1=freq;

//<statements>

endmodule目的是产生一个周期为5个时钟周期的方波。

(3)仿真验证

可以不进行仿真,如需进行参考(教程)

(4)管脚分配

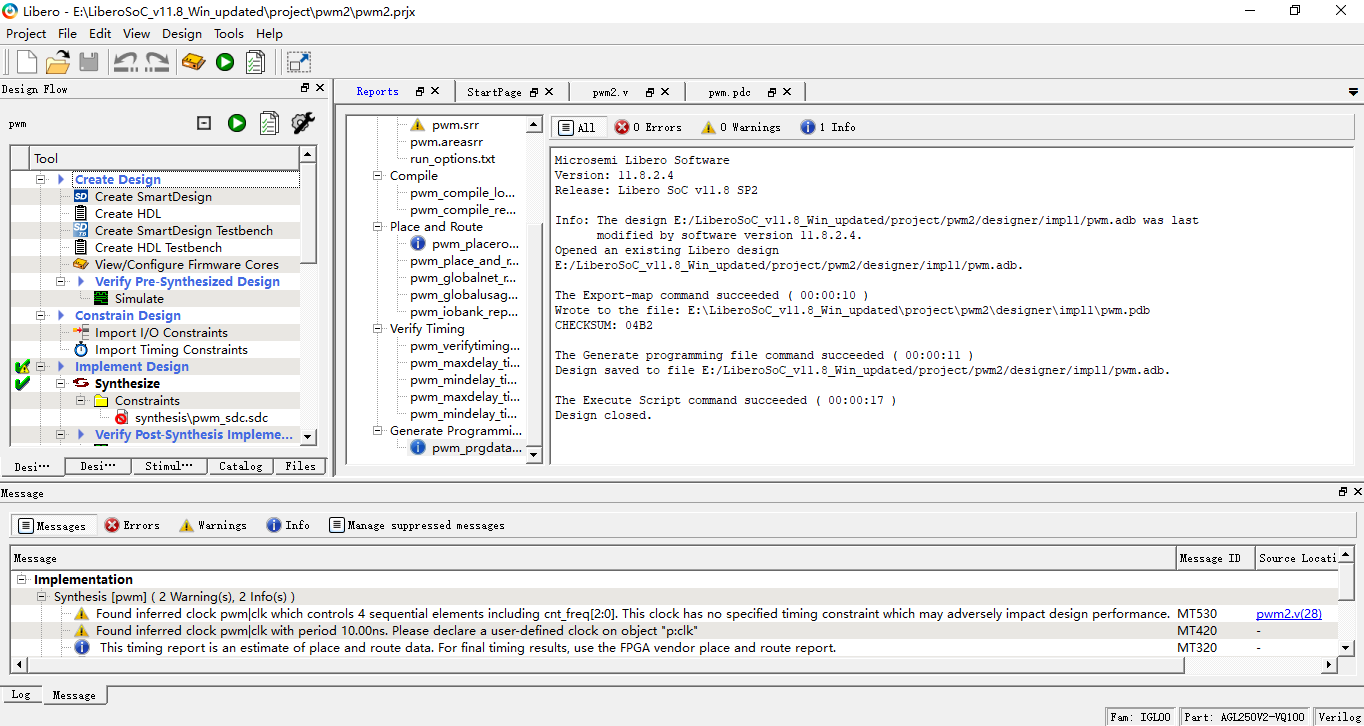

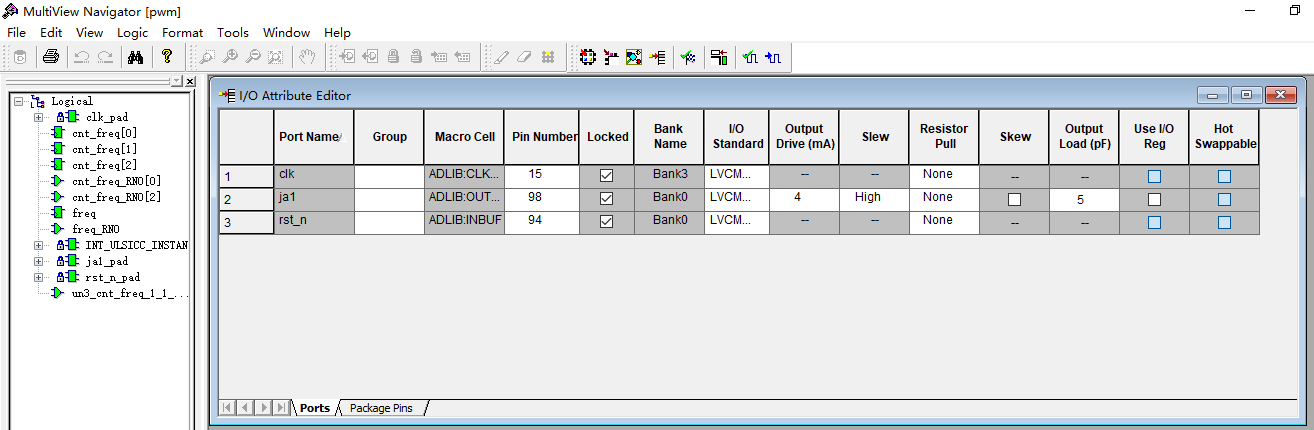

双击Create/Edit I/O Attributes,打开图形化配置界面,在打开之前,Libero会先进行综合(Synthesize)、编译(Complie),当都运行通过时,才会打开配置界面。

管脚具体分配参见数据手册或者原理图

特别注意:分配完管脚之后一定要先按屏幕左上角File下面的commit and check,然后回到designer界面,选择Designer窗口下的File->Export->Constraint File,会导出一个xxx.pdc文件,保存在工程目录下的constraint文件夹,导出文件后一定要File->save保存,这样在主界面就可以找到配置好的xxx.pdc文件了

(5)继续执行

直接点击Generate Programming Data ,如果没有报错会生成一个xxx.pdb文件,文件目录是./designer/impl/xxx.pdb。

(6)程序烧写

运用Flashpro软件,连接FlashPro下载器和开发板的JTAG接口。Flashpro下载器有接口的一侧连接JTAG的1号管脚的那一侧,也就是开发板的外侧。

首先下载一些需要的软件和帮助文档

1)请务必先注册百度网盘用户,安装网盘客户端软件。务必拷贝链接到浏览器,再拷贝密码(提取码),将资料保存到您的百度云中,最后在百度网盘客户端软件中下载。

使用浏览器下载,会导致解压失败。严禁使用浏览器下载!!

2)严禁直接点击链接或敲键盘输入密码!严禁使用其他下载软件(如迅雷)!!

Actel Flashpro5下载线使用说明书

链接:https://pan.baidu.com/s/1MeJ57Va1W-wvxoBX6tulgw

提取码:hb3z

如果是仅仅烧写,请请下载这个链接

烧写软件Flashpro_V11.5

(默认安装,无需破解,内含下载线驱动。)

链接:https://pan.baidu.com/s/10qXg24zlTPZVsXz5Y5x9Mw

提取码:blg8

下载完配置好之后打开Flashpro软件,选择New Project新建工程,然后点击Configure Device—>Browse找到刚刚创建的xxx.pdb,右边的模式可以选择Program,Verify或者Erase进行程序烧入Flash,核实程序或擦除程序。连接FlashPro下载器和开发板的JTAG接口,最后点击Program烧写程序。

(7)实验结果

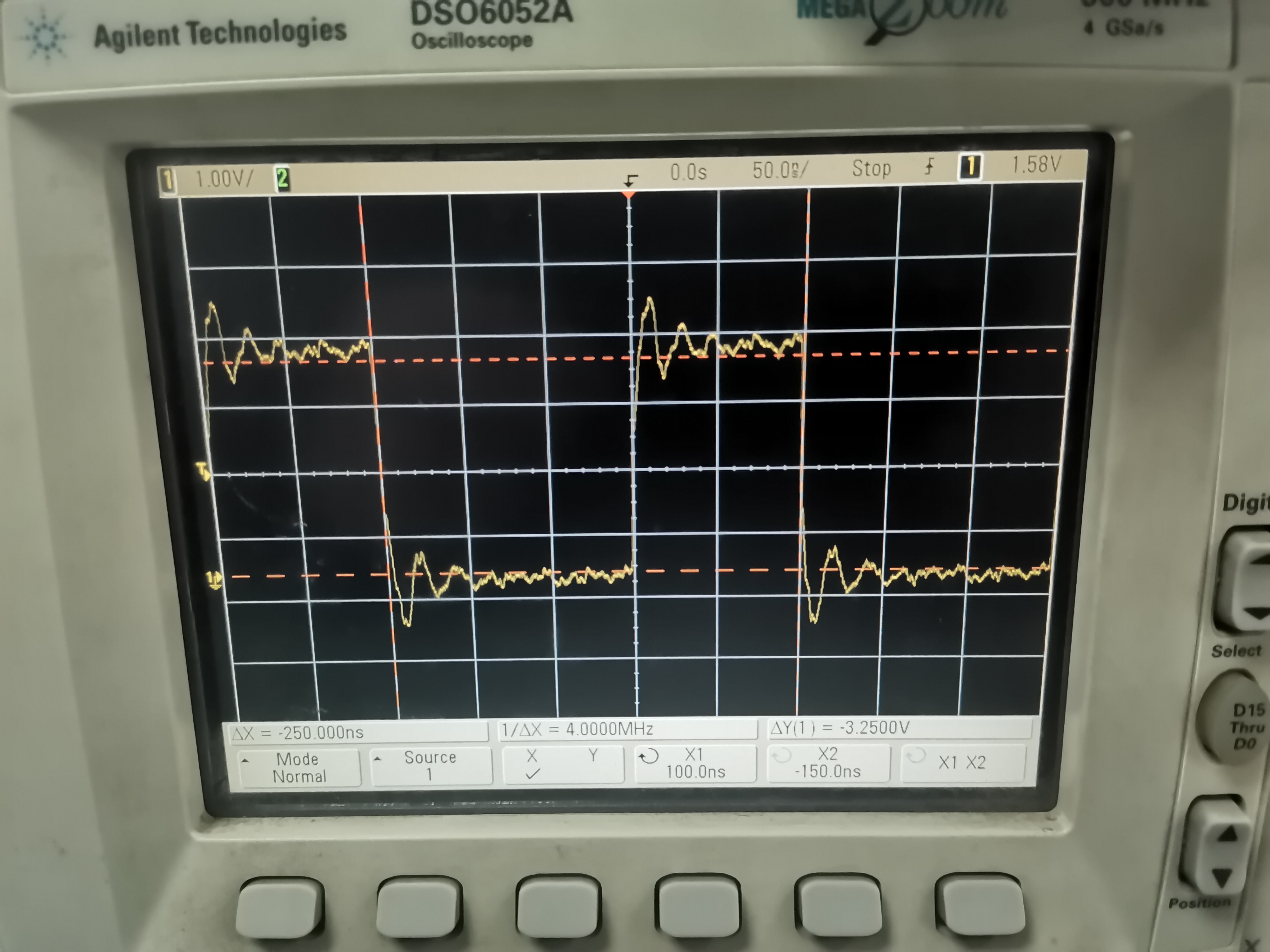

由于tag的内部时钟为20MHz,程序是一个5的计数器,因此产生了一个4MHz的方波如图所示。烧写完程序后无需其他的控制,只需要Zedboard供电就可以产生方波了。

实验的经验总结:

tag的时钟对应原理图中的OSC,不是CLK;- 管脚分配与

vivado不同在于只改xxx.pdb没有用,必须通过designer更改,然后保存才有用; - 晶振的数据手册:

ASTX-H11; - 晶振输出对应的管脚是U8的3号管脚。